Improved performance of on-chip data interconnects

Trading off the reliability, crosstalk delay and power dissipation on on-chip buses are challenging issue for the design community in Deep Sub Micron (DSM) and very deep beneath Micron Technologies (VDSM). To improve the overall system performance it is necessary to reduce and scaling technology to control these effects data on-chip interconnects. Error Correcting Codes (ECC) have been used on the data buses to increase the reliability of the data transfer on the bus on-chip data with penalty of overhead power, delay and area. The dynamic power dissipation of interconnects depends on supply voltage, operating clock frequency, load capacitance and switching activity. All the parameters which influence the dynamic power dissipation are technology dependent except switching activity. Dynamic power dissipation has been reduced by reducing the switching activity. The switching activity has been reduced by adopting a data encoding technique on data interconnects. Encoding the data on it interconnects the promising technique to decrease the dynamic power dissipation and total on-chip delay on the buses and hence overall system performance can be increased.

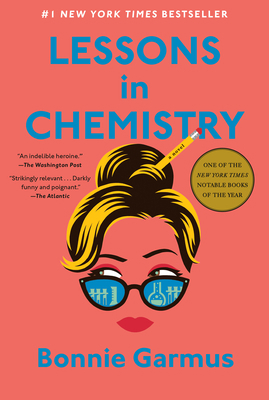

Format:Paperback

Language:English

ISBN:620267248X

ISBN13:9786202672481

Release Date:June 2020

Publisher:LAP Lambert Academic Publishing

Length:156 Pages

Weight:0.52 lbs.

Dimensions:0.4" x 6.0" x 9.0"

Based on Your Recent Browsing

Customer Reviews

customer rating | review

There are currently no reviews. Be the first to review this work.